SpaceCube

electrical and electronics

SpaceCube (GSC-TOPS-35)

A Family of Reconfigurable Hybrid On-Board Science Data Processors

Overview

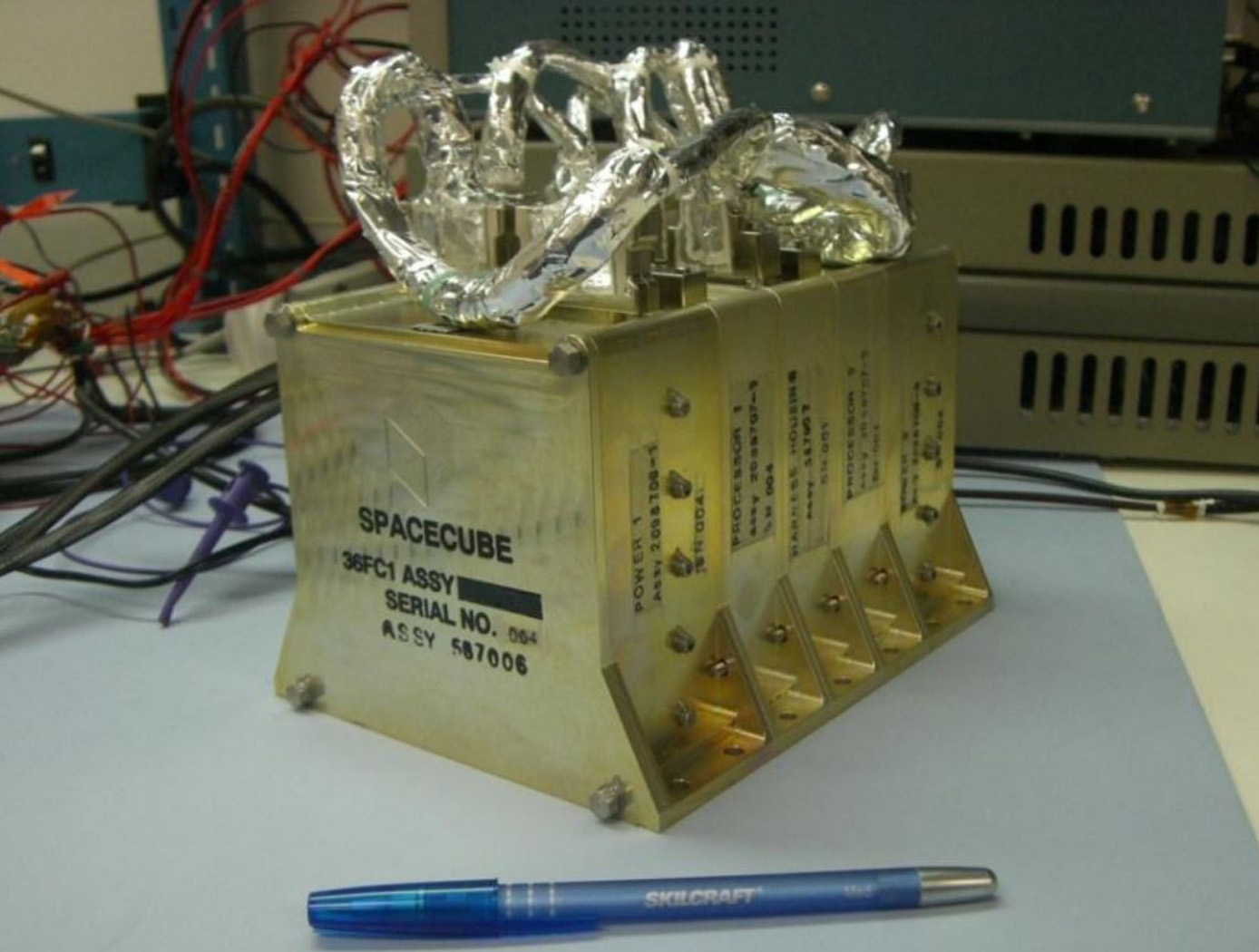

SpaceCube is a cross-cutting, in-flight reconfigurable Field Programmable Gate Array (FPGA) based on-board hybrid science data processing system developed at the NASA Goddard Space Flight Center (GSFC). The goal of the SpaceCube program is to provide 10x to 100x improvements in on-board computing power while lowering relative power consumption and cost. The SpaceCube design strategy incorporates commercial radiation-tolerant Xilinx Virtex FPGA technology and couples it with an integrated upset detection and correction architecture to provide reliable order of magnitude improvements in computing power over traditional fully radiation-hardened flight systems.

The Technology

Next generation instruments are capable of producing data at rates of 108 to 1011 bits per second, and both their instrument designs and mission operations concepts are severely constrained by data rate/volume. SpaceCube is an enabling technology for these next generation missions.

SpaceCube has demonstrated enabling capabilities in Earth Science, Planetary, Satellite Servicing, Astrophysics and Heliophysics prototype applications such as on-board product generation, intelligent data volume reduction, autonomous docking/landing, direct broadcast products, and data driven processing with the ability to autonomously detect and react to events. SpaceCube systems are currently being developed and proposed for platforms from small CubeSats to larger scale experiments on the ISS and standalone free-flyer missions, and are an ideal fit for cost constrained next generation applications due to the tremendous flexibility (both functional and interface compatibility) provided by the SpaceCube system.

Benefits

- 10x to 100x more on-board computing power than current radiation-hardened space processors

- Efficient and low cost: SpaceCube allows for relative power consumption and cost to be dramatically lowered in comparison with alternatives

Applications

- Real-time SAR / Lidar / Image Processing

- Autonomous Operations / Robotic Servicing

- On-Board Product Generation

- Real-time Event / Feature Detection

- Real-time Wavefront Sensing and Control

- On-Board Data Volume Reduction

- Real-time Situational Awareness

- Intelligent Data Compression

- Real-time Calibration / Correction

- On-Board Classification

- Inter-platform Collaboration

Similar Results

SpaceCube 3.0 Mini Processor Card

The SpaceCube 3.0 Mini Processor Card represents orders of magnitude increase in performance and capability over typical radiation-hardened processor-based systems and significant advances over the previous generation of SpaceCube technology. The primary processing engine of the card is a radiation-tolerant FPGA. This processor card is very low weight, can fit within the 1U CubeSat form-factor (10cm x 10cm x 10cm), and will be low power. Much of the SpaceCube 2.0 Micro design is incorporated into the SpaceCube 3.0 Mini design. In addition, lessons learned from the SpaceCube 2.0 Mini card are applied. Instead of using a rigid-flex design, the SC3.0 Mini uses a backplane architecture. The processor card plugs into a backplane that routes signals to other card slots. In order to meet the numerous high-speed I/O interfaces required by the latest generation science instruments and applications, a high-density backplane connector is needed. The SpaceCube 3.0 Mini uses a high-density connector to plug into the backplane. The FPGA has flash memory attached that is used for storing algorithm and application code for any hosted soft processors. The processor card also has a nanominiature front-panel connector that adds even more I/O to support instrument interfaces such as Camera Link or SpaceWire.

The SpaceCube 3.0 Mini Processor Card features a rad-tolerant FPGA, but the radiation mitigation can be tailored for harsher environments by adding an external rad-hard device that configures and monitors the FPGA over the backplane. The processor card pushes transceiver quantity, routing, and performance for spaceflight. The card is designed to fit in the compact 1U CubeSat form factor. The SpaceCube 3.0 Mini supports scalability by networking multiple processor cards together.

SpaceCube 3.0 Flight Processor Card

SpaceCube 3.0 features the rad-tolerant multi-core T2080 processor and the rad-tolerant Kintex UltraScale FPGA. The SpaceCube 3.0 Flight Processor Card meets the industry standards in lightweight systems specifications. In addition, the flight processor card can be installed with an expansion card option to allow a tightly-coupled, mission unique card to be installed. The mission unique expansion card can support a variety of capabilities to make SpaceCube 3.0 a powerful instrument processor, including A/D converters, D/A converters, gigabit ethernet, and additional co-processors. Furthermore, the flight processor card is extremely flexible. Algorithms can be implemented in both the Kintex UltraScale FPGA and the T2080 processor. More sequential portions of the algorithm can be implemented quickly and efficiently on the processor, while other algorithms that are more parallel in nature and computation heavy can be accelerated in the FPGA. Using a hybrid system, each can be optimally implemented to take advantage of the features of both.

The SpaceCube 3.0 Flight Processor Card design consists mostly of NASA-qualified flight parts and has many features to mitigate radiation effects on the processor system. The processor card can configure the FPGA to scrub configuration memory. In addition, it can monitor the health of the processors, the FPGA, and any coprocessors on the expansion card using watchdog timers. The FPGA uses error detection and multiple redundant copies to mitigate against radiation upsets to the configuration files, which are stored in external non-volatile memories.

Unique Datapath Architecture Yields Real-Time Computing

The DLC platform is composed of three key components: a NASA-designed field programmable gate array (FPGA) board, a NASA-designed multiprocessor on-a-chip (MPSoC) board, and a proprietary datapath that links the boards to available inputs and outputs to enable high-bandwidth data collection and processing.

The inertial measurement unit (IMU), camera, Navigation Doppler Lidar (NDL), and Hazard Detection Lidar (HDL) navigation sensors (depicted in the diagram below) are connected to the DLC’s FPGA board. The datapath on this board consists of high-speed serial interfaces for each sensor, which accept the sensor data as input and converts the output to an AXI stream format. The sensor streams are multiplexed into an AXI stream which is then formatted for input to a XAUI high speed serial interface. This interface sends the data to the MPSoC Board, where it is converted back from the XAUI format to a combined AXI stream, and demultiplexed back into individual sensor AXI streams. These AXI streams are then inputted into respective DMA interfaces that provide an interface to the DDRAM on the MPSoC board. This architecture enables real-time high-bandwidth data collection and processing by preserving the MPSoC’s full ability.

This sensor datapath architecture may have other potential applications in aerospace and defense, transportation (e.g., autonomous driving), medical, research, and automation/control markets where it could serve as a key component in a high-performance computing platform and/or critical embedded system for integrating, processing, and analyzing large volumes of data in real-time.

Power Processing Unit (PPU) for Small Spacecraft Electric Propulsion

Key subsystems of a scalable PPU for low-power Hall effect electric propulsion have been developed and demonstrated at NASA GRC. The PPU conditions and supplies power to the thruster and propellant flow control (PFC) components. It operates from an input voltage of 24 to 34 VDC to be compatible with typical small spacecraft with 28 V unregulated power systems. The PPU provides fault protection to protect the PPU, thruster, PFC components, and spacecraft. It is scalable to accommodate various power and operational requirements of low-power Hall effect thrusters. An important subsystem of a PPU is the discharge supply, which processes up to 95% of the power in the PPU and must process high voltage to accelerate thrust generating plasma. Each discharge power module in this PPU design is capable of processing up to 500 W of power and output up to 400 VDC. A full-bridge topology operating at switching frequency 50 kHz is used with a lightweight foil transformer. Two or more modules can operate in parallel to scale up the discharge power as required. Output voltage and current regulation controls allow for any of the common thruster start-up modes (hard, soft or glow).

High-Speed, Low-Cost Telemetry Access from Space

NASA's SDR uses Field-Programmable Gate Array (FPGA) technology to enable flexible performance on orbit. A first-generation FM-modulated transceiver is capable of operating at up to 1 Mbps downlink and 50 kbps uplink, full duplex. An FPGA performs Reed-Solomon (255,223) encoding, decoding, and bit synchronization, providing Consultative Committee for Space Data Systems (CCSDS) and Near Earth Network (NEN) telemetry protocol compatibility. The transceiver accepts data from the onboard flight computer via a source synchronous RS422 interface.

NASA's second-generation full duplex SDR, known as PULSAR (programmable ultra-lightweight system-adaptable radio, Figures 1 and 2 below) incorporates command receiver and telemetry transmitters, as well as updated processing and power capabilities. An S-band command receiver offers a max uplink data rate of 300 Kbps and built-in QPSK demodulation. X- and S-Band telemetry transmitters offer a max downlink data rate of 150 Mbps and flexible forward-error correction (FEC) using Reed-Solomon encoding (LDPC rate 7/8 and 1/2 convolution in development), and it uses QPSK modulation. The use of FEC adds an order of magnitude increase in telemetry throughput due to an improved coding gain. An onboard FPGA uses high-speed logic for uplink/downlink and encoding/decoding processes. Balloon flight testing has been conducted and is ongoing for PULSAR.