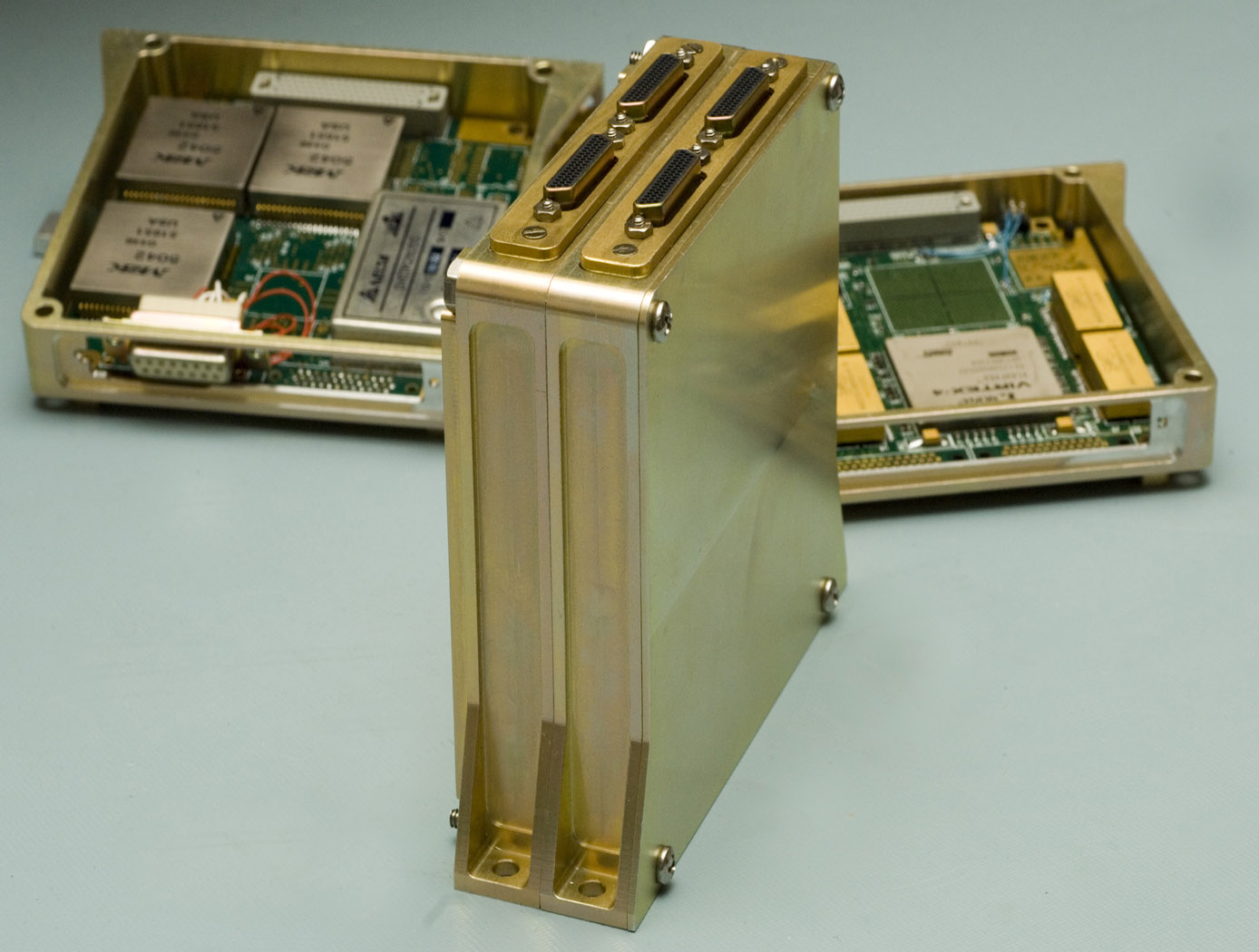

SpaceCube v2.0 Processor with DDR2 Memory Upgrade

instrumentation

SpaceCube v2.0 Processor with DDR2 Memory Upgrade (GSC-TOPS-243)

Greater memory throughput to support the next generation of instruments.

Overview

The DDR SDRAM memory dies that had been radiation tested and flight qualified have reached end of life. The remaining stock of DDR SDRAM is rapidly dwindling and future projects will require a change to DDR2 SDRAM. Additionally, the next generation of instruments are set to produce even greater amounts of science data and require even more memory bandwidth for on-board processing. Switching to DDR2 improves support for new instruments because it can provide more than a 2x memory speedup over the DDR1 design.

The Technology

This new version of the card assembly will feature a total of eight 4x DDR2 SDRAM memories per Xilinx FPGA. A dedicated regulator was included to compensate for the lower operating voltage of DDR2 in comparison to the older DDR memory. The DDR2 memories are grouped in pairs with shared address/command/control lines. By sharing those lines, the number of Xilinx I/Os for the DDR2 interfaces could be reduced. These improvements extend the life and design of the processor and provide even greater memory throughput to support the next generation of instruments.

Benefits

- Greater memory bandwidth for on-board processing and image processing applications

- RAM operates at lower voltage

Applications

- Onboard computing / processing for satellites and spacecraft

Similar Results

First Stage Bootloader

The First Stage Bootloader reads software images from flash memory, utilizing redundant copies of the images, and launches the operating system. This bootloader finds a valid copy of the OS image and the ram filesystem image in flash memory. If none of the copies are fully valid, the bootloader attempts to construct a fully valid image by validating the images in small sections and piecing together validated sections from multiple copies.

Periodically, throughout this process, the First Stage Bootloader restarts the watchdog timer.

The First Stage Bootloader reads a boot table from a default location in flash memory. This boot table describes where to find the OS image and its supporting ram filesystem image in flash. It uses header information and a checksum to validate the table. If the table is corrupt, it reads the next copy until it finds a valid table. There can be many copies of the table in flash, and all will be read if necessary. The First Stage Bootloader reads the ram filesystem image into memory and validates its contents. Similar to the boot table, if one copy of the image is corrupt, it will read the remaining copies until it finds one with a valid header. If it doesn't find a valid copy, it will break the image down into smaller portions. For each section, it checks each copy until it finds a valid copy of the section and copies the valid section into a new copy of the image. The First Stage Bootloader reads the OS image and interprets it. If anything in the image is corrupt, it reads the remaining copies until it finds a fully valid copy. If no copy is fully valid, it will use individual valid records from multiple copies to create a fully valid image.

SpaceCube 3.0 Flight Processor Card

SpaceCube 3.0 features the rad-tolerant multi-core T2080 processor and the rad-tolerant Kintex UltraScale FPGA. The SpaceCube 3.0 Flight Processor Card meets the industry standards in lightweight systems specifications. In addition, the flight processor card can be installed with an expansion card option to allow a tightly-coupled, mission unique card to be installed. The mission unique expansion card can support a variety of capabilities to make SpaceCube 3.0 a powerful instrument processor, including A/D converters, D/A converters, gigabit ethernet, and additional co-processors. Furthermore, the flight processor card is extremely flexible. Algorithms can be implemented in both the Kintex UltraScale FPGA and the T2080 processor. More sequential portions of the algorithm can be implemented quickly and efficiently on the processor, while other algorithms that are more parallel in nature and computation heavy can be accelerated in the FPGA. Using a hybrid system, each can be optimally implemented to take advantage of the features of both.

The SpaceCube 3.0 Flight Processor Card design consists mostly of NASA-qualified flight parts and has many features to mitigate radiation effects on the processor system. The processor card can configure the FPGA to scrub configuration memory. In addition, it can monitor the health of the processors, the FPGA, and any coprocessors on the expansion card using watchdog timers. The FPGA uses error detection and multiple redundant copies to mitigate against radiation upsets to the configuration files, which are stored in external non-volatile memories.

SpaceCube Mini Solid State Data Recorder (SSDR)

NASA's SpaceCube Mini SSDR is a 3.5”x3.5” card designed for use in CubeSats and SmallSats. The SSDR uses a radiation-tolerant field programmable gate array (FPGA) that interfaces with two independently controlled and powered banks of NAND Flash storage, providing up to 12 Terabits of storage capacity. The card includes multiple SpaceWire nodes and multi-gigabit transceivers for commanding and data transfer, various error prevention and correction mechanisms including Reed-Solomon encoding/decoding and data randomization schemes, and depacketizers/packetizers for handling data in CCSDS format.

This NASA technology is innovative in its combination of high reliability for harsh radiation environments (e.g., geostationary orbit, lunar orbit and surface, etc.) with high-speed data transfer capabilities (400+ MB/s write, 600+ MB/s read) in a compact form factor. The design allows for selective population of NAND Flash modules and independent control of memory banks, enabling power optimization through features like single-bank operation. The card integrates with a modular architecture system in which multiple CubeSat-sized cards (e.g., processors, GPS, etc.) can be mixed and matched to meet specific mission requirements. The SSDR card includes radiation-hardened voltage regulators to ensure safe operation in space environments.

The SSDR is ideal for small form factor satellites with some combination of the following requirements: (a) ability to store large amounts of data generated by high-performance detectors and sensors for extended durations (e.g., in environments without nearby relay capabilities), (b) ability to read and write data with high throughput, and (c) ability to operate in harsh radiation environments. It is fully compatible with NASA’s CubeSat Card Specification (CS2) and NASA’s SpaceCube v3.0 mini processing card, which is also available for licensing.

High-Speed, Low-Cost Telemetry Access from Space

NASA's SDR uses Field-Programmable Gate Array (FPGA) technology to enable flexible performance on orbit. A first-generation FM-modulated transceiver is capable of operating at up to 1 Mbps downlink and 50 kbps uplink, full duplex. An FPGA performs Reed-Solomon (255,223) encoding, decoding, and bit synchronization, providing Consultative Committee for Space Data Systems (CCSDS) and Near Earth Network (NEN) telemetry protocol compatibility. The transceiver accepts data from the onboard flight computer via a source synchronous RS422 interface.

NASA's second-generation full duplex SDR, known as PULSAR (programmable ultra-lightweight system-adaptable radio, Figures 1 and 2 below) incorporates command receiver and telemetry transmitters, as well as updated processing and power capabilities. An S-band command receiver offers a max uplink data rate of 300 Kbps and built-in QPSK demodulation. X- and S-Band telemetry transmitters offer a max downlink data rate of 150 Mbps and flexible forward-error correction (FEC) using Reed-Solomon encoding (LDPC rate 7/8 and 1/2 convolution in development), and it uses QPSK modulation. The use of FEC adds an order of magnitude increase in telemetry throughput due to an improved coding gain. An onboard FPGA uses high-speed logic for uplink/downlink and encoding/decoding processes. Balloon flight testing has been conducted and is ongoing for PULSAR.

SpaceCube 3.0 Mini Processor Card

The SpaceCube 3.0 Mini Processor Card represents orders of magnitude increase in performance and capability over typical radiation-hardened processor-based systems and significant advances over the previous generation of SpaceCube technology. The primary processing engine of the card is a radiation-tolerant FPGA. This processor card is very low weight, can fit within the 1U CubeSat form-factor (10cm x 10cm x 10cm), and will be low power. Much of the SpaceCube 2.0 Micro design is incorporated into the SpaceCube 3.0 Mini design. In addition, lessons learned from the SpaceCube 2.0 Mini card are applied. Instead of using a rigid-flex design, the SC3.0 Mini uses a backplane architecture. The processor card plugs into a backplane that routes signals to other card slots. In order to meet the numerous high-speed I/O interfaces required by the latest generation science instruments and applications, a high-density backplane connector is needed. The SpaceCube 3.0 Mini uses a high-density connector to plug into the backplane. The FPGA has flash memory attached that is used for storing algorithm and application code for any hosted soft processors. The processor card also has a nanominiature front-panel connector that adds even more I/O to support instrument interfaces such as Camera Link or SpaceWire.

The SpaceCube 3.0 Mini Processor Card features a rad-tolerant FPGA, but the radiation mitigation can be tailored for harsher environments by adding an external rad-hard device that configures and monitors the FPGA over the backplane. The processor card pushes transceiver quantity, routing, and performance for spaceflight. The card is designed to fit in the compact 1U CubeSat form factor. The SpaceCube 3.0 Mini supports scalability by networking multiple processor cards together.